Serviços de fabricação eletrônica completos, ajudam você a obter facilmente seus produtos eletrônicos de PCB e PCBA

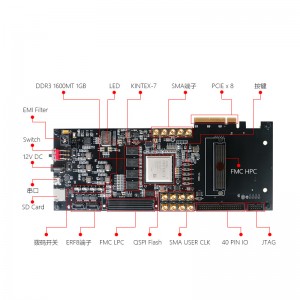

Comunicação de fibra óptica FPGA Xilinx K7 Kintex7 PCIe

- DDR3 SDRAM: 16 GB DDR3 barramento de 64 bits, taxa de dados de 1600 Mbps

- QSPI Flash: Um pedaço de QSPIFLASH de 128 mbit, que pode ser usado para arquivos de configuração de FPGA e armazenamento de dados do usuário

- Interface PCLEX8: A interface PCLEX8 padrão é usada para comunicação com a interface PCIE da placa-mãe do computador. Ela suporta o padrão PCI Express 2.0. A taxa de comunicação de canal único pode chegar a 5 Gbps.

- Porta serial USB UART: Uma porta serial, conecte ao PC através do cabo miniusb para realizar a comunicação serial

- Cartão Micro SD: o cartão MicroSD acomoda todo o caminho, você pode conectar o cartão MicroSD padrão

- Sensor de temperatura: um chip sensor de temperatura LM75, que pode monitorar a temperatura ambiente ao redor da placa de desenvolvimento

- Porta de extensão FMC: um FMC HPC e um FMCLPC, que podem ser compatíveis com várias placas de expansão padrão

- Terminal de conexão de alta velocidade ERF8: 2 portas ERF8, que suportam transmissão de sinal de ultra-alta velocidade Extensão de 40 pinos: reservou uma interface IO de extensão geral com 40 pinos de 2,54 mm, O efetivo tem 17 pares, suporta 3,3 V

- A conexão periférica do nível e do nível de 5 V pode conectar os periféricos periféricos de diferentes interfaces 1O de uso geral

- Terminal SMA; 13 cabeças SMA banhadas a ouro de alta qualidade, o que é conveniente para os usuários cooperarem com placas de expansão FMC AD/DA de alta velocidade para coleta e processamento de sinais

- Gerenciamento de Clock: Fonte multi-clock. Inclui a fonte de clock diferencial do sistema de 200 MHz SIT9102.

- Oscilação de cristal diferencial: cristal de 50 MHz e chip de gerenciamento de relógio programável SI5338P: também equipado com

- 66MHz EMCCLK. Pode se adaptar com precisão a diferentes frequências de clock de uso

- Porta JTAG: 10 pontos Porta JTAG padrão de 2,54 mm, para download e depuração de programas FPGA

- Chip de monitoramento de tensão de sub-reinicialização: um pedaço do chip de monitoramento de tensão ADM706R e o botão com o botão fornece um sinal de reinicialização global para o sistema

- LED: 11 luzes LED, indicam a alimentação da placa, sinal config_done, FMC

- Sinal indicador de energia e 4 LEDs de usuário

- Chave e interruptor: 6 chaves e 4 interruptores são botões de reinicialização do FPGA,

- O botão do programa B e 4 teclas do usuário são compostos por 4 interruptores de acionamento duplo de faca única

Escreva sua mensagem aqui e envie para nós

Categorias de produtos

-

Telefone

-

E-mail

-

Whatsapp

-

Skype

-

Skype

-

Skype